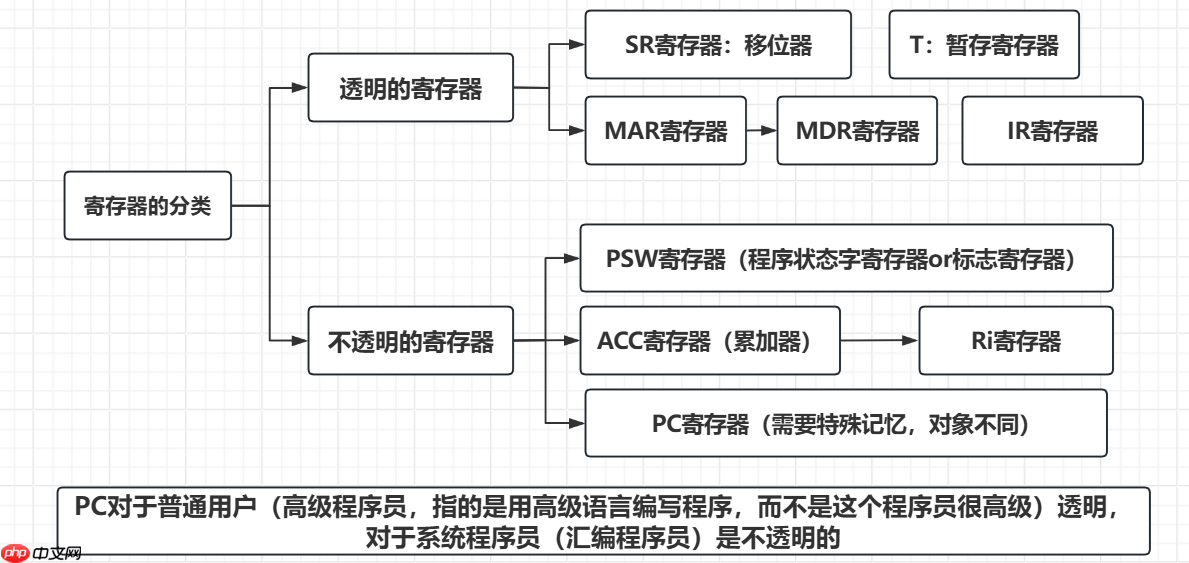

前文对“透明性”的解释有误:所谓透明或不透明,关键在于普通用户能否直接对其进行修改;

Ri代表的是通用寄存器集合,这里特别强调:暂存器其实就是锁存器!!!!!!!!!!

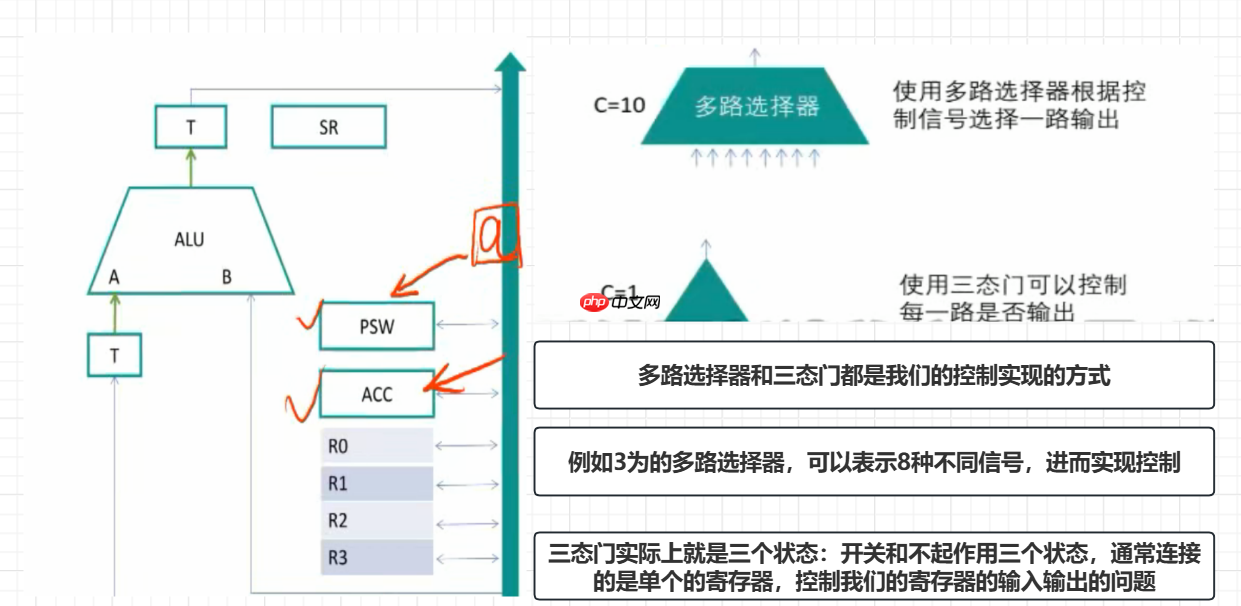

### 2.控制信号的两种实现方式

### 2.控制信号的两种实现方式

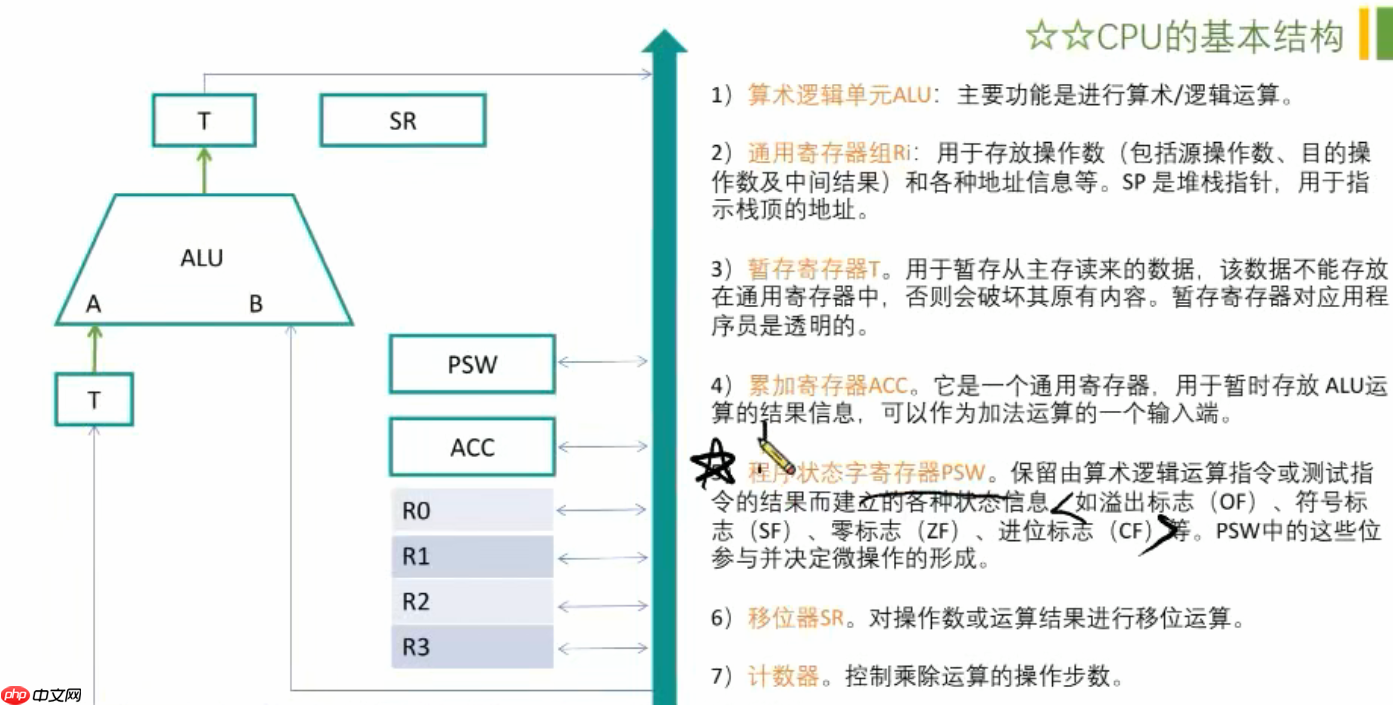

### 3.运算单元与控制单元图示解析

### 3.运算单元与控制单元图示解析

下图展示的是运算器结构,相关功能说明均已标注在图中,内容清晰明了;

需记住的是图中的T——即暂存寄存器(也称锁存器),它在该结构中设置了两个位置:

接下来是控制器部分:图中注释详尽,易于理解;

接下来是控制器部分:图中注释详尽,易于理解;

微操作信号发生器(也称为CU)由三个输入决定,即图中指向它的三条线路;

注意MAR与MDR之间的通信方向:一个是单向,一个是双向;

ID为指令译码器,负责将指令翻译成控制信号,不属于寄存器范畴。

### 4.单指令周期与单周期CPU的区别

### 4.单指令周期与单周期CPU的区别

单指令周期:所有指令执行耗时相同;

单周期CPU:每条指令仅用一个时钟周期完成,无论复杂与否,CPI恒为1(Clocks Per Instruction)。

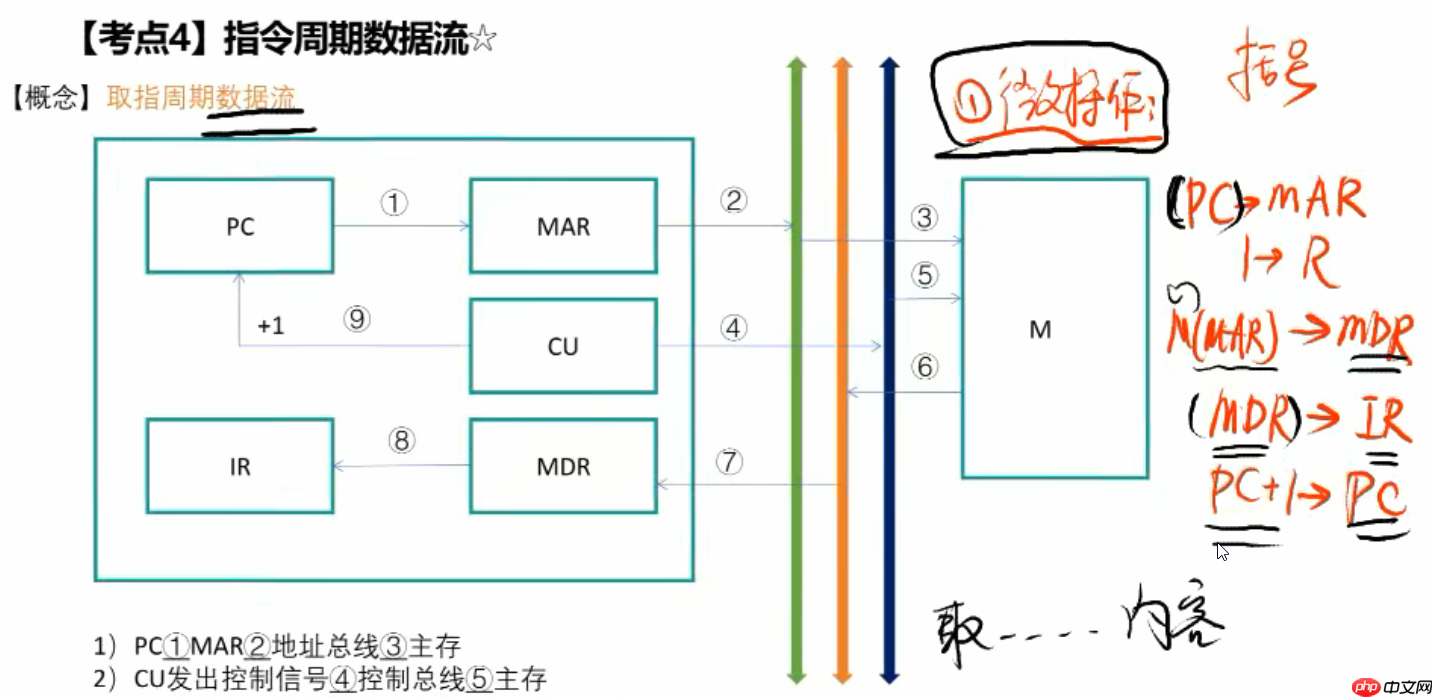

带括号的操作表示读取括号内寄存器的内容;

#### 5.2 指令分析阶段的数据流

#### 5.2 指令分析阶段的数据流

AD(IR) 中的 AD 表示地址码(Address),即从指令寄存器IR中提取出地址字段;

执行完毕后,MDR中存放的是有效地址 EA(Effective Address);

#### 5.3 中断处理阶段的数据流

#### 5.3 中断处理阶段的数据流

SP为栈顶指针,图示流程对应中断响应过程中“断点保护”这一环节;

中断处理三步曲:关中断 → 保存断点 → 跳转至中断服务程序;

其中,“关中断”由硬件自动完成无需编程干预,而中断服务程序本质仍是程序,由多条指令构成,其执行属于软件行为。

至于为何SP要先减1,初学者可能困惑,可参考如下分步理解:

至于为何SP要先减1,初学者可能困惑,可参考如下分步理解:

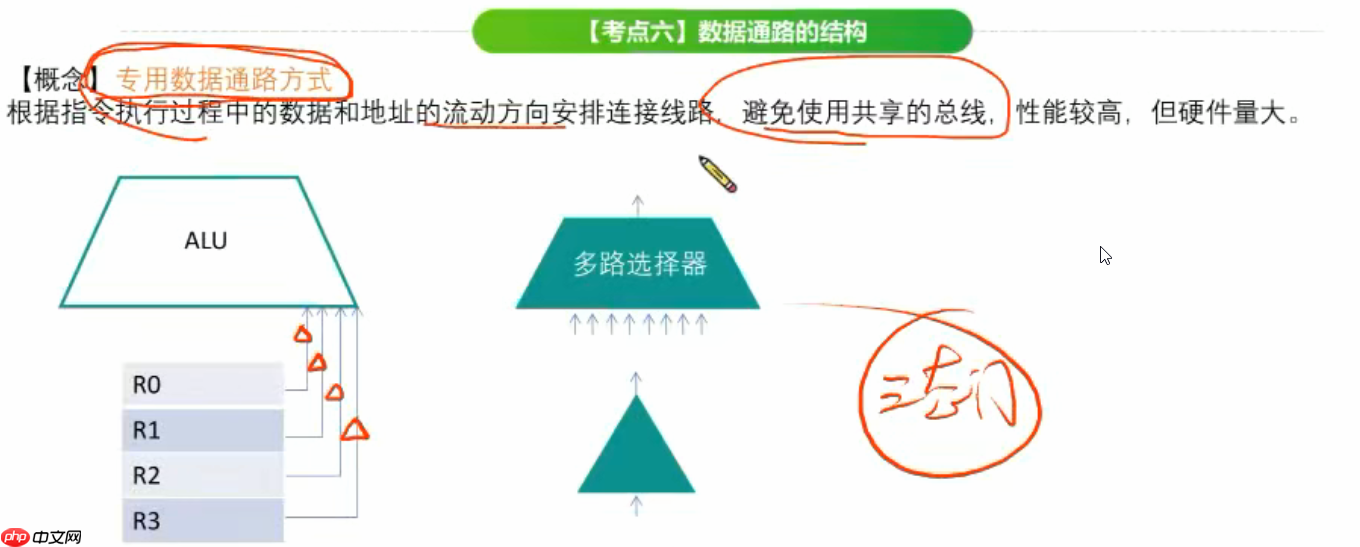

本节重点区分三种数据传输结构:单总线、三总线、专用通路;

### 7.中断向量表机制详解

### 7.中断向量表机制详解

下图为中断与异常的分类示意:

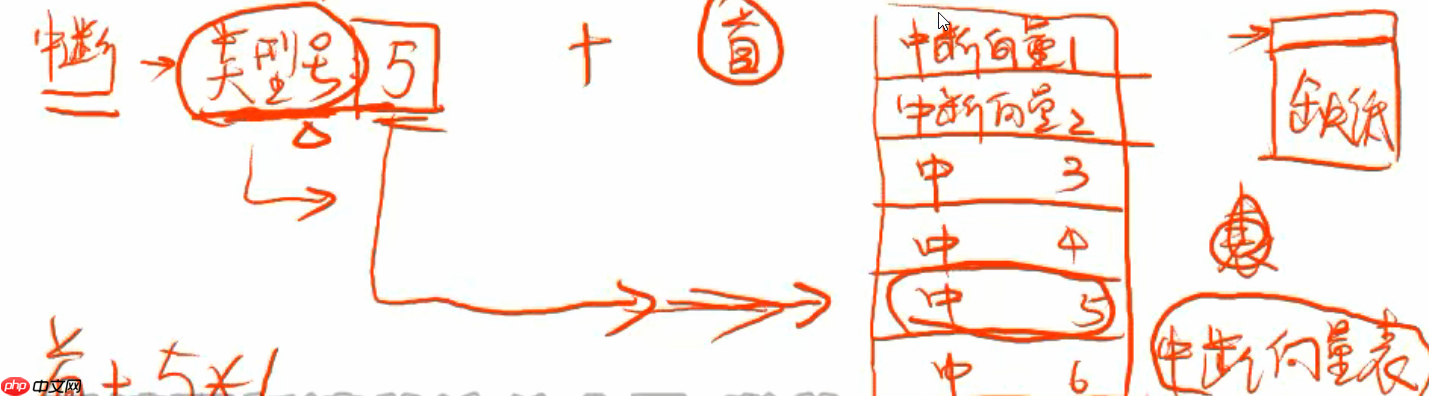

当中断发生时,系统首先获得中断类型号,据此查表找到对应中断服务程序入口地址,进而跳转执行;

当中断发生时,系统首先获得中断类型号,据此查表找到对应中断服务程序入口地址,进而跳转执行;

中断为何说是软硬件协同?原因如下:

中断为何说是软硬件协同?原因如下:

1)硬件层面:中断隐指令自动完成关中断、保存断点、跳转入口等工作,这不是程序员写的指令,而是CPU内置机制; 2)软件层面:真正的中断服务程序由操作系统或用户编写,运行时由软件驱动;

因此,整个中断处理过程体现了软硬件的高度协作。

以上就是组成原理精讲课---运算器控制器和数据通路的搭建的详细内容,更多请关注php中文网其它相关文章!

每个人都需要一台速度更快、更稳定的 PC。随着时间的推移,垃圾文件、旧注册表数据和不必要的后台进程会占用资源并降低性能。幸运的是,许多工具可以让 Windows 保持平稳运行。

Copyright 2014-2025 https://www.php.cn/ All Rights Reserved | php.cn | 湘ICP备2023035733号