10月11日,复旦大学集成芯片与系统全国重点实验室、集成电路与微纳电子创新学院的周鹏-刘春森团队宣布,继今年4月发布“破晓(pox)”皮秒闪存器件后,时隔半年再次取得重大突破——成功研发出“长缨(cy-01)”闪存架构。

该架构实现了二维超快闪存器件与成熟硅基CMOS工艺的深度融合,成功研制出全球首款二维-硅基混合架构闪存芯片。这一成果标志着二维材料存储技术从实验室原型迈向工程化应用的关键一步。

相关论文以《全功能二维-硅基混合架构闪存芯片》(A full-featured 2D flash chip enabled by system integration)为题,于北京时间10月8日晚发表在国际顶级学术期刊《自然》(Nature)上。

封装后的二维-硅基混合架构闪存芯片(带PCB板)

今年4月,该团队已在《自然》发表“破晓(PoX)”二维闪存原型器件,实现400皮秒级超高速非易失性存储,创下当时全球最快的半导体电荷存储纪录。然而,如何将这一前沿器件融入现有半导体制造体系,成为推进产业化的关键挑战。

“破晓(PoX)”皮秒闪存器件

研究团队指出,加速新技术落地必须依托成熟的CMOS产线。CMOS作为当前集成电路制造的核心工艺,拥有完整的产业链支撑。为此,团队历经五年持续攻关,在器件设计、材料集成和工艺兼容等方面逐一突破。

核心难点在于:如何在不损害二维材料优异性能的前提下,将其与硅基CMOS电路高效集成?

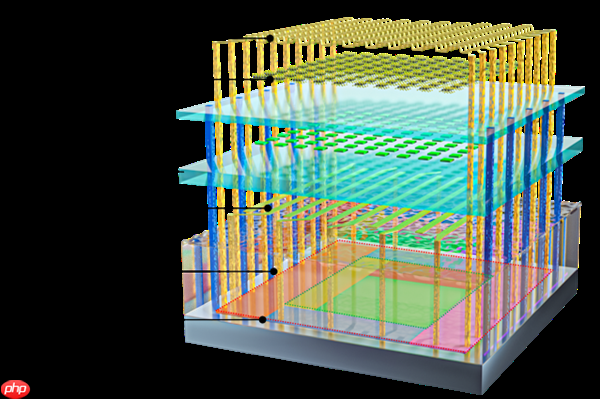

团队创新性地利用二维材料本身具备的柔性特性,采用模块化集成策略——先分别独立制备二维存储单元和CMOS控制电路,再通过微米尺度通孔的高密度单片互连技术,实现两者的三维集成。

这一关键技术突破,使得原子级薄的二维材料能与传统硅基衬底实现紧密贴合,同时保持高达94.3%的良率。

在此基础上,团队提出了一套跨平台系统设计方法论,涵盖二维-CMOS协同设计、接口协议统一等环节,并将这套完整的系统集成方案命名为“长缨(CY-01)架构”。

测试结果显示,基于CMOS控制二维存储核心的完整芯片支持8-bit指令操作、32-bit高速并行读写及随机寻址功能,整体性能远超当前主流Flash闪存技术,首次实现二维-硅基混合架构的全功能芯片验证。

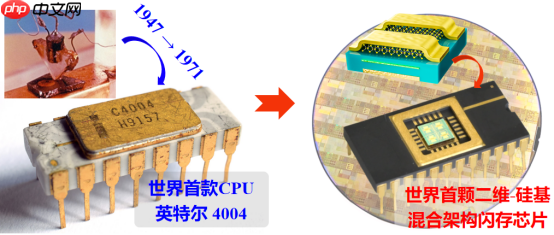

世界首颗二维-硅基混合架构闪存芯片:左侧为半导体晶体管从原型器件到第一款CPU。右侧为二维闪存器件结构、8英寸流片CMOS晶圆、二维-硅基混合架构闪存芯片

二维-硅基混合架构闪存芯片光学显微镜照片

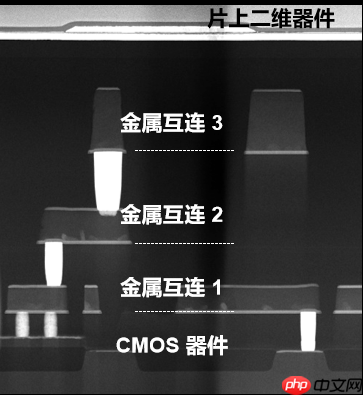

二维-硅基混合架构闪存芯片透射电子显微镜照片

二维-硅基混合架构闪存芯片结构示意图,包含二维模块、CMOS控制电路和微米尺度通孔

下一步,团队计划建设专用实验平台,联合相关机构推进自主可控的工程化项目,目标在3至5年内将该技术扩展至兆比特规模。期间所产生的知识产权和IP核将面向合作企业开放授权,推动产业化进程。

以上就是碾压传统闪存!我国研发全球首个二维-硅基混合架构闪存芯片的详细内容,更多请关注php中文网其它相关文章!

每个人都需要一台速度更快、更稳定的 PC。随着时间的推移,垃圾文件、旧注册表数据和不必要的后台进程会占用资源并降低性能。幸运的是,许多工具可以让 Windows 保持平稳运行。

Copyright 2014-2025 https://www.php.cn/ All Rights Reserved | php.cn | 湘ICP备2023035733号