本篇重点探讨在使用vivado进行仿真时,对gsr信号的理解及其可能带来的影响。

当我们在vivado中完成FPGA设计代码与测试激励的编写后,点击“Run Simulation”以启动modelsim等仿真工具进行验证。

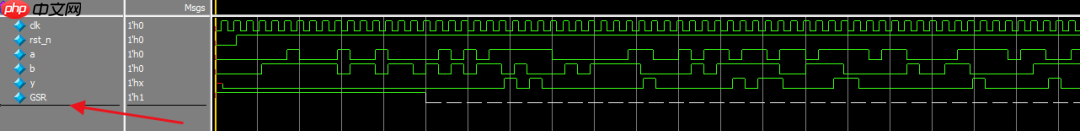

此时,在波形窗口中除了能看到自己定义的信号外,还会观察到一个名为GSR的信号。该信号初始为1,大约在100ns时刻由高变低,呈现为一条虚线。

这个信号从何而来?

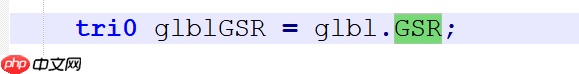

实际上,vivado在启动仿真流程时,会自动加载一个名为glbl.v的系统级模块文件。而GSR信号正是在这个全局模块中被声明并驱动的。

它会对仿真结果产生影响吗?

通常情况下,许多工程师会选择直接隐藏或忽略该信号,认为其存在与否不影响功能验证。然而,这种做法在某些场景下可能会掩盖潜在问题。

那么GSR到底有何作用?难道只是一个冗余信号?

直到一次进行时序仿真(post-layout simulation)时,发现了一个异常现象:

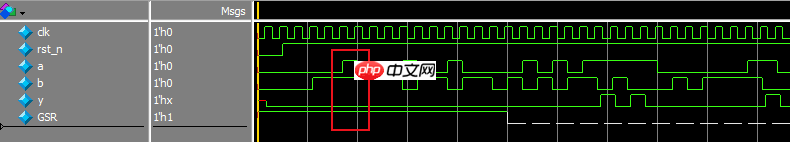

图中所示为两个信号a、b经过一个与门输出y的逻辑路径,且其前级是异步复位寄存器。在GSR仍为高电平期间,尽管a和b均已稳定为高电平,但y并未如预期输出高电平;而当GSR变为0之后,电路行为恢复正常。

这表明:问题很可能出在GSR上。

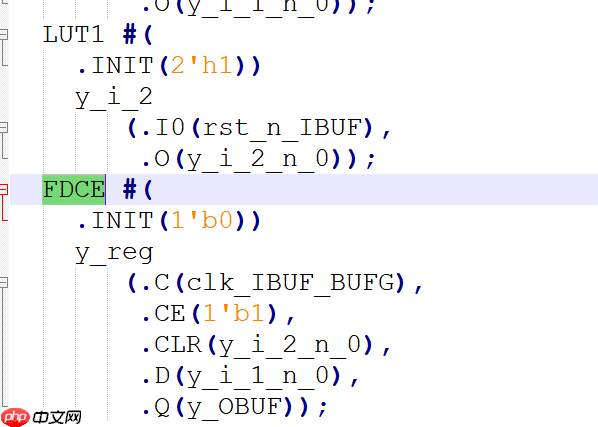

进一步查看时序仿真的网表文件可知,此时所仿真的并非原始RTL代码,而是综合、实现后由FPGA底层原语构成的门级网表。

(提示:后仿真使用的是映射到实际器件结构的网表文件)

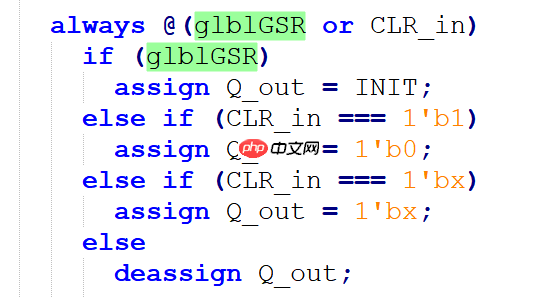

深入查找相关元件模型(位于Xilinx的unisims库中),可以找到FDCE触发器的仿真模型定义。

继续查看FDCE内部实现细节:

可以看出,FDCE的行为受GSR信号控制——在GSR为高期间,无论D输入如何变化,Q输出都将被强制维持在初始状态(通常是0),直到GSR释放(拉低)后,寄存器才开始正常响应时钟和数据输入。

这就解释了前述bug的原因:即使用户复位已经释放,只要GSR仍处于激活状态(高电平),寄存器依然无法更新其输出。

该如何应对这种情况?

解决方案有两种思路:一是调整GSR拉低的时间点(不推荐),二是将有效激励信号的施加时间推迟至GSR释放之后。

建议做法:在进行仿真(尤其是时序仿真)时,确保所有关键信号(包括复位信号)的有效动作延迟至少100ns以上,即避开GSR的默认有效周期。

简要总结GSR的作用机制:它是FPGA内部的一个全局复位信号,用于在上电或配置完成后统一初始化所有寄存器。

在vivado仿真环境中,GSR信号的存在对于准确模拟FPGA真实启动过程至关重要。仿真器会在t=0时刻自动激活GSR一段时间(约100ns),以此模拟硬件上电后配置完成前的全局清零阶段。随后GSR自动释放,用户设计中的逻辑(包括用户自定义复位逻辑)才能真正开始运行。

因此,在波形中关注glbl.GSR的变化时机,以及各寄存器在此期间的状态转换,是验证系统启动顺序和复位可靠性的关键环节。

除非有特殊调试目的,否则不应随意屏蔽或修改GSR的默认行为,否则可能导致仿真与实际硬件行为不一致。

以上就是vivado进行仿真时,GSR信号的理解和影响的详细内容,更多请关注php中文网其它相关文章!

每个人都需要一台速度更快、更稳定的 PC。随着时间的推移,垃圾文件、旧注册表数据和不必要的后台进程会占用资源并降低性能。幸运的是,许多工具可以让 Windows 保持平稳运行。

Copyright 2014-2025 https://www.php.cn/ All Rights Reserved | php.cn | 湘ICP备2023035733号