cadence 基于ucie™标准的封装ip在三星5nm汽车工艺上成功完成首次流片,标志着cadence持续致力于提供满足新一代汽车电子和高性能计算应用严格要求的高性能车规级ip解决方案。

☞☞☞AI 智能聊天, 问答助手, AI 智能搜索, 免费无限量使用 DeepSeek R1 模型☜☜☜

Cadence的UCIe IP在最高16GT/s速率及所有支持的低速率下均实现全功能运行,眼图质量和误码率(BER)远超规范要求。此性能验证了设计的稳健性和可靠性,可轻松集成到对能效和可靠性要求极高的汽车电子和数据中心应用中。

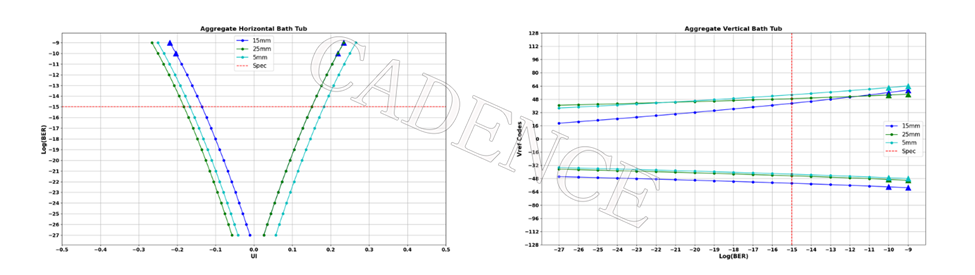

图1:16GT/s速度下,所有信道长度均展现卓越性能,大幅超出UCIe规范要求。

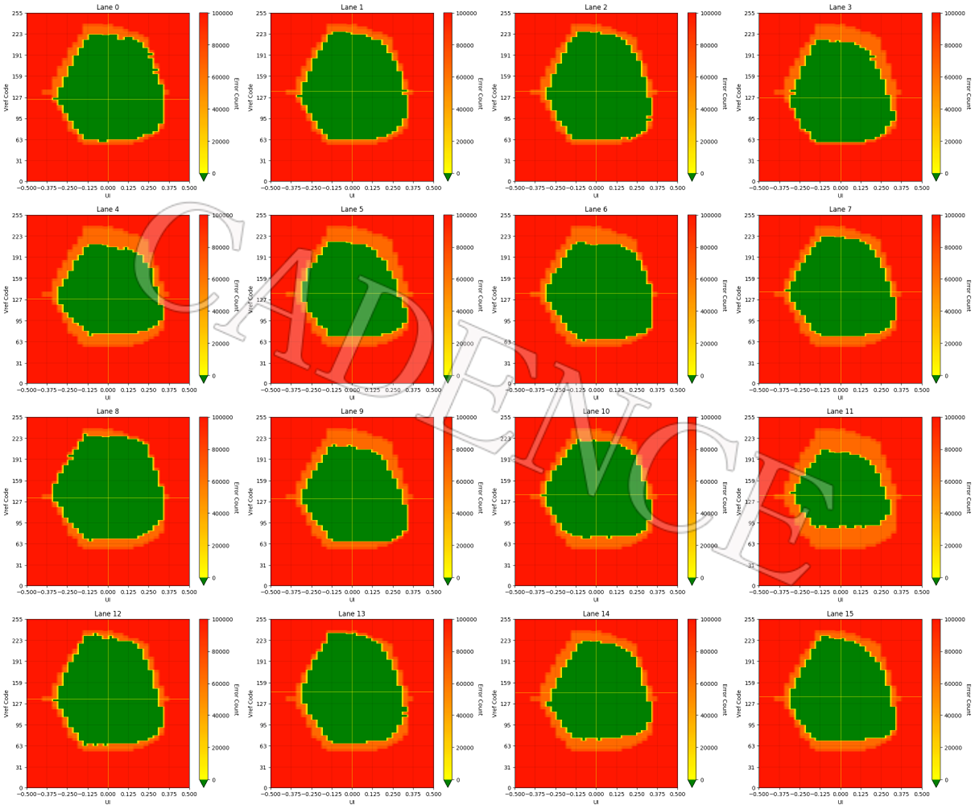

图1的浴盆曲线显示,相位插值器和Vref在1e-15规范要求下(红色虚线)的眼图性能,在短、中、长芯片间距下均表现出优异的接收器性能。图2展示了使用PRBS检查器测量的接收器眼图,PRBS模式在UCIe信道上以最大速度持续传输。硬件成功启动和训练流程确保所有通道均呈现完全打开的眼图。

图2:16GT/s下PRBS模式,所有通道显示良好的接收眼图。

该PHY支持16Tx和16Rx标准封装的全双工通信互联,最大距离达25mm。经过各种距离和布线方法的广泛测试验证了其性能。该PHY基于三星5nm汽车工艺实现,符合UCIe规范和严格的汽车行业要求。在对HPC/AI/ML应用至关重要的多芯片设计中,PHY可在芯片间提供低功耗、低延迟的无缝通信,从而支持高性能计算(HPC)应用。

图3:Cadence是UCIe核心成员之一,积极参与制定包括汽车领域在内的技术规范。

为补充PHY,Cadence提供各种配置的UCIe控制器产品组合。从原始流接口到完整的PCIe协议,以及轻量级、高效的AXI、CXS.B和CHI-C2C接口,Cadence均提供支持。我们的控制器产品组合具有多种配置,包括UCIe-CXS和UCIe-AXI,并已获得SGS的ASIL-B车规认证。交付前,控制器和PHY可在IP子系统中无缝合并,并在各级进行广泛验证,提供简便的集成体验,使客户能够专注于SoC差异化设计。

Cadence与三星晶圆代工持续合作,为双方共同客户提供业界领先的IP解决方案,助力加速创新,将新一代汽车和高性能计算系统推向市场。

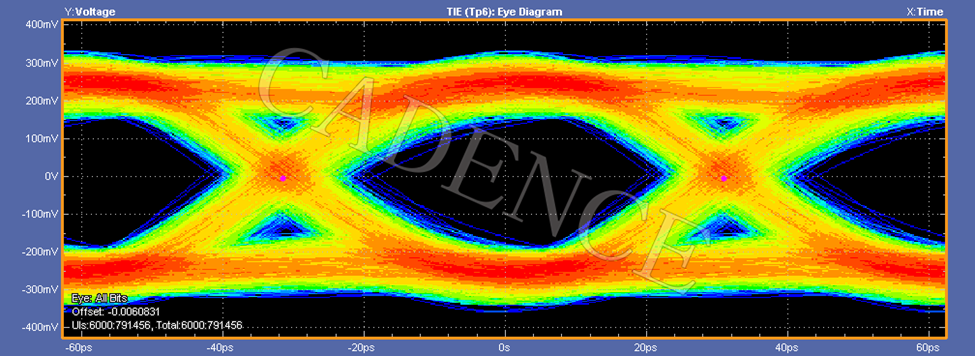

图4:示波器显示16GT/s下的UCIe Tx眼图。

Cadence将继续突破互联和系统性能的界限,欲了解更多Cadence UCIe产品信息,请点击此处。

以上就是Cadence UCIe IP 在 Samsung Foundry 的 5nm 汽车工艺上实现流片成功的详细内容,更多请关注php中文网其它相关文章!

每个人都需要一台速度更快、更稳定的 PC。随着时间的推移,垃圾文件、旧注册表数据和不必要的后台进程会占用资源并降低性能。幸运的是,许多工具可以让 Windows 保持平稳运行。

Copyright 2014-2025 https://www.php.cn/ All Rights Reserved | php.cn | 湘ICP备2023035733号